|

|

||

|---|---|---|

| lib | ||

| .gitignore | ||

| LF_VIZ.png | ||

| README.md | ||

| risc-v_shell.tlv | ||

| risc-v_solutions.tlv | ||

README.md

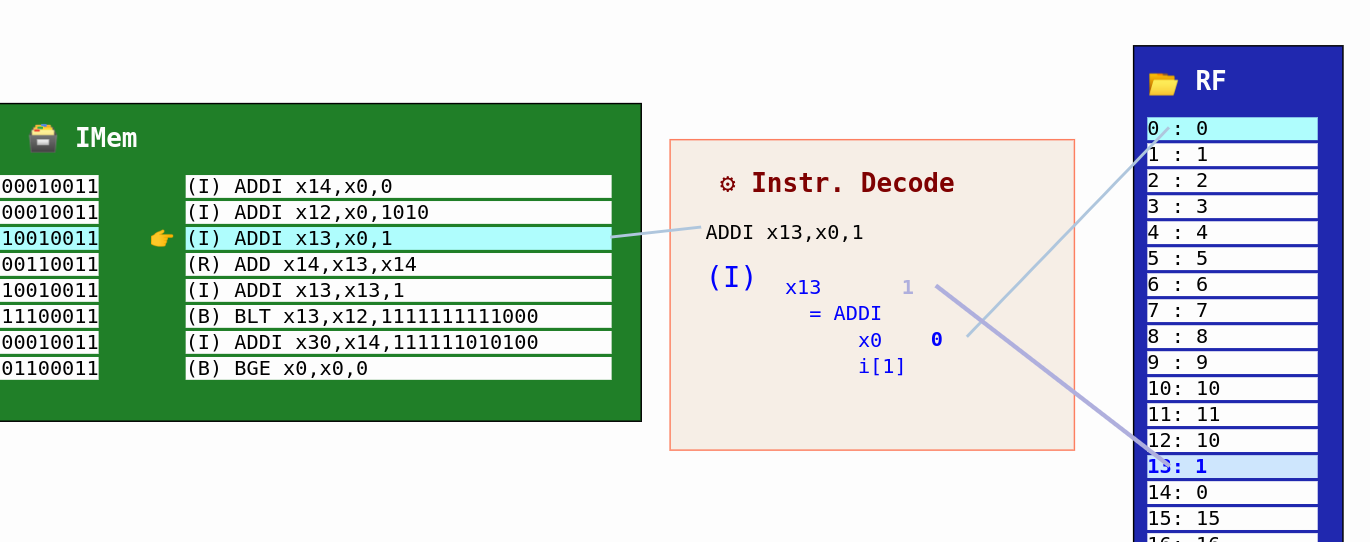

Building a RISC-V CPU Core

Accompanying resources for the Building a RISC-V CPU Core EdX course by Steve Hoover of Redwood EDA, Linux Foundation, and RISC-V International.

Welcome

Congratulations for taking this step to expand your knowledge of computer hardware.

At this time, there are no course corrections or platform issues to report. Please do let us know within the EdX platform if anything gets in your way. There's a great deal of infrastructure to maintain for the course, and we aim to keep it all running smoothly. Now, back to EdX.

RISC-V Starting-Point Code

To begin the first RISC-V lab, when instructed to do so, Ctrl-click this link to open starting-point code in makerchip.

RISC-V Reference Solution

In case you get stuck, we've got your back! These reference solutions (Ctrl-click) will help with syntax, etc. without handing you the answers.

Here's a pre-built logic diagram of the final CPU. Ctrl-click here to explore in its own tab.

Finished!

Congratulations!!!

After completing this course, we hope you are inspired to continue your journey. These ideas might help:

- Try the tutorials in Makerchip.

- Learn more about TL-Verilog.

- Explore the RISC-V ecosystem.

- Take other courses from Linux Foundation

- Discover other training from Redwood EDA

- Get your core running on real hardware using FPGAs in the cloud or on your desktop.

- Install TL-Verilog tools.

- Learn about the WARP-V TL-Verilog CPU core generator.